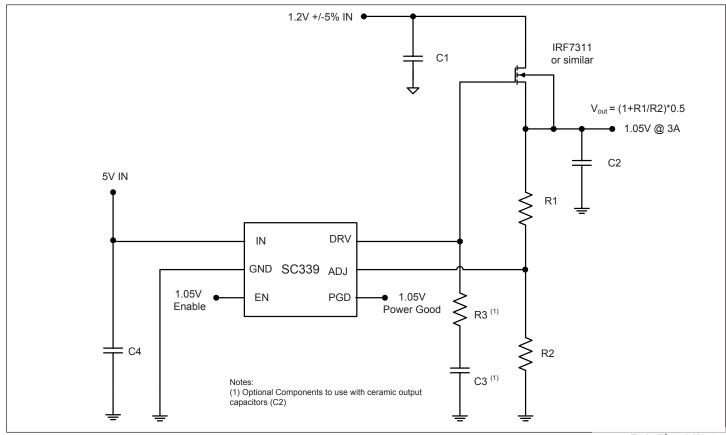

Typical Application Circuit

#### Description

The SC339 is an ultra-low output voltage, linear power supply controller designed to simplify power management for notebook PCs. It is part of Semtech's Smart LDO<sup>TM</sup> family of products. The SC339 has a user adjustable output that can be set anywhere between 0.5V and 3.3V using two external resistors.

SC339 features include tight output voltage regulation ( $\pm$  1% over 0°C to +85°C), enable control, open drain power good signal, under-voltage protection and soft-start. The wenable pin allows the part to enter a very low power standby mode. Pulling it high enables the output. The power good pin is an open drain and asserts low when the voltage at the adjust pin is below 88% (typ) of nominal. If the voltage at the adjust pin is below 50% (typ) of nominal, the under-voltage protection circuitry will shut down the output. The SC339 is available in a tiny SOT-23 6-pin surface mount package.

#### Features

- ± 1% Voltage Accuracy Over-Temperature

- Low Shutdown Current

- Runs Off 5V Supply

- Ultra-Fast Transient Response

- Enable Control for the Output

- Power Good Monitoring and Signaling for the Output

- Gate Drive from Input Supply Enables Use of N-Channel MOSFET

- User Selectable Dropout Voltage

- Under-Voltage Protection for the Output

- SOT-23 6-pin Surface Mount Package

- Compatible with Ceramic Capacitors

- Low Ripple Output

- Internal 1ms soft-start requires no external components

- Fully WEEE and RoHS compliant

#### Applications

- Notebook PCs

- Desktop Computers

- Battery Powered Devices

- Portable Instruments

## Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. Exposure to absolute maximum rated conditions for extended periods of time may affect device reliability.

| Parameter                             | Symbol                              | Maximum                        | Units |

|---------------------------------------|-------------------------------------|--------------------------------|-------|

| Input Supply Voltage                  | V <sub>IN</sub>                     | -0.3 to +6                     | V     |

| Drive Pin                             | V <sub>DRV</sub>                    | -0.3 to V <sub>IN</sub> + 0.3V | V     |

| Adjust and Power Good Pin             | V <sub>ADJ</sub> , V <sub>PGD</sub> | -0.3 to V <sub>IN</sub> + 0.3V | V     |

| Enable Pin                            | V <sub>EN</sub>                     | -0.3 to V <sub>IN</sub> + 0.3V | V     |

| Thermal Impedance Junction to Ambient | $\theta_{JA}$                       | 190                            | °C/W  |

| Thermal Impedance Junction to Case    | $\theta_{JC}$                       | 81                             | °C/W  |

| Operating Ambient Temperature Range   | T <sub>A</sub>                      | -40 to +85                     | °C    |

| Operating Junction Temperature Range  | TJ                                  | -40 to +125                    | °C    |

| Storage Temperature Range             | T <sub>stg</sub>                    | -65 to +150                    | °C    |

| Lead Temperature (Soldering) 10 Sec.  | T <sub>LEAD</sub>                   | 300                            | °C    |

| ESD Rating (Human Body Model)         | V <sub>ESD</sub>                    | 2                              | kV    |

#### **Electrical Characteristics**

Unless specified:  $T_A = 25 \degree C$ ,  $V_{IN} = V_{EN} = 5V \pm 5\%$ ,  $V_{PWR}^{(1)} = 1.5V \pm 5\%$ ,  $OA \le I_{OUT} \le 3A$ . Values in **bold** apply over full operating ambient temperature range.

| Parameter                  | Symbol              | Conditions              | Min | Тур  | Max | Units |

|----------------------------|---------------------|-------------------------|-----|------|-----|-------|

| Supply Voltage             | V <sub>IN</sub>     |                         | 4.5 | 5    | 5.5 | V     |

| Quiescent Current          | Ι <sub>Q</sub>      | V <sub>IN</sub> = 5V    |     | 130  | 200 | μA    |

| Standby Current            | I <sub>Q(OFF)</sub> | EN low                  |     | 0.1  | 1.0 | μA    |

| Input Under-Voltage Lockou | t                   |                         | ·   |      |     |       |

| Start Threshold            | V <sub>UVLO</sub>   | $V_{IN}$ rising         |     | 4.20 |     | V     |

| Hysteresis                 | V <sub>HYST</sub>   | V <sub>IN</sub> falling |     | 0.10 |     | V     |

| EN                         |                     |                         |     |      |     |       |

| Fuchie land Threehold      | V <sub>IH</sub>     | Output on               | 2.8 |      |     |       |

| Enable Input Threshold     | V <sub>IL</sub>     | Output off              |     |      | 1.8 | - V   |

| Enable Input Bias Current  |                     | $V_{IN} = V_{EN} = 5V$  | -1  |      | +1  | μA    |

## SEMTECH

## **POWER MANAGEMENT**

## **Electrical Characteristics**

| Parameter                                              | Symbol               | Conditions                                            | Min  | Тур   | Max  | Units             |

|--------------------------------------------------------|----------------------|-------------------------------------------------------|------|-------|------|-------------------|

| ADJ                                                    | 1                    | 1                                                     | 1    | 1     | 1    |                   |

| Adjust Input Bias Current                              | I <sub>ADJ</sub>     | V <sub>ADJ</sub> = 0.5V                               | -100 | 0     | +100 | nA                |

| Reference Voltage                                      | V <sub>ADJ</sub>     | $0^{\circ}C \le T_{A} \le +85^{\circ}C$               | -1%  | 0.500 | 1%   | V                 |

| DRV                                                    | 1                    | -                                                     |      | 1     | 1    |                   |

| QutputsCurrent.om                                      | I <sub>DRV</sub>     | Sourcing                                              | 5    | 20    |      | mA                |

|                                                        |                      | Sinking                                               | 5    | 20    |      | mA                |

| Output Voltage                                         | V <sub>DRV</sub>     | Full On, I <sub>DRV</sub> = 0mA, V <sub>IN</sub> = 5V | 4.70 | 4.85  |      | V                 |

| Output Under-Voltage Protect                           | ion                  |                                                       | -1   |       | 1    | -                 |

| Trip Threshold <sup>(2)</sup>                          | V <sub>TH(UV)</sub>  | Measured at ADJ pin                                   | 40   | 50    | 60   | %V <sub>ADJ</sub> |

| PGD                                                    | 1                    | -                                                     | -    |       | 1    | -                 |

| Power Good Threshold <sup>(3)</sup>                    | V <sub>TH(PGD)</sub> | Measured at ADJ pin                                   | -15  | -12   | -8   | %V <sub>ADJ</sub> |

| Output Logic Low Voltage                               | V <sub>PGD</sub>     | V <sub>ADJ</sub> = 0.4V, I <sub>PGD</sub> = -1mA      |      |       | 0.4  | V                 |

| Power Good<br>Leakage Current                          | I <sub>PGD</sub>     | $V_{ADJ} = 0.5V, \ 0V \le V_{PGD} \le V_{IN}$         | -1   | 0     | +1   | μA                |

| Soft-Start                                             |                      |                                                       |      |       | -    |                   |

| Output Rise Time 10% VOUT<br>to 90% VOUT, VOUT = 1.05V | t,                   | From EN rising to<br>99% of V <sub>out</sub>          | 500  | 1000  | 2000 | μs                |

Notes:

1)  $V_{PWR}$  = input voltage to pass device drain (or source depending upon orientation of FET). 2) If  $V_{TH(UV)}$  is exceeded for longer than 1ms (nom.) the protection circuitry will shut down the output. 3) During start-up only,  $V_{TH(PGD)}$  is -6% (typical), then switches to -12% (typical).

## SEMTECH

## POWER MANAGEMENT

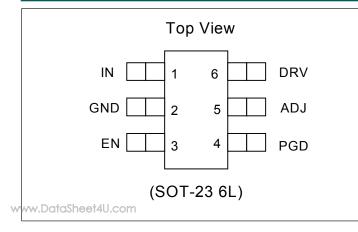

## Pin Configuration

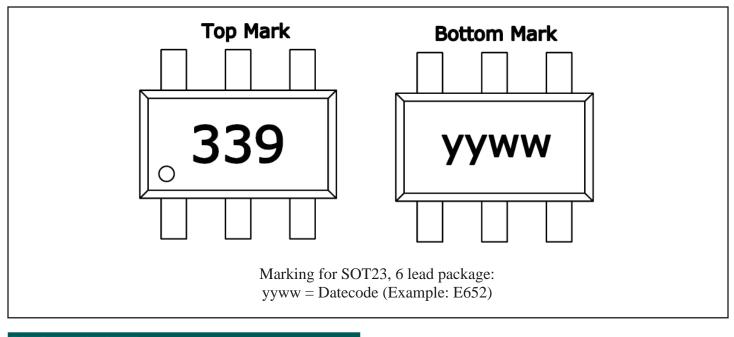

## Marking Information

## Ordering Information

| Part Number | Package          |

|-------------|------------------|

| SC339SKTRT  | SOT-23 6 Pin     |

| SC339EVB    | Evaluation Board |

#### Notes:

1) Only available in tape and reel packaging. A reel contains 2500 devices.

3)  $V_{ADJ}^{"}$  is ± 1% over 0°C ≤  $T_A$  ≤ +85°C.

4) Lead-free product. This product is fully WEEE and RoHS compliant.

| Pin Desci | riptions |                                                                                                                            |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------|

| Pin       | Pin Name | Pin Function                                                                                                               |

| 1         | IN       | 5V supply                                                                                                                  |

| 2         | GND      | Ground                                                                                                                     |

| 3         | EN       | Active high enable control - connect to IN if not being used - do not allow to float                                       |

| 4         | PGD      | Power good signal output for $V_{_{\rm OUT}}$                                                                              |

| 5         | ADJ      | Regulator sense input - used for sensing the output voltage for power good and under-voltage and to set the output voltage |

| 6         | DRV      | Output of regulator - drives the gate of an N-channel MOSFET to maintain $V_{_{\rm OUT}}$ set by R1 and R2                 |

|           |          | www.DataSheet4li.com                                                                                                       |

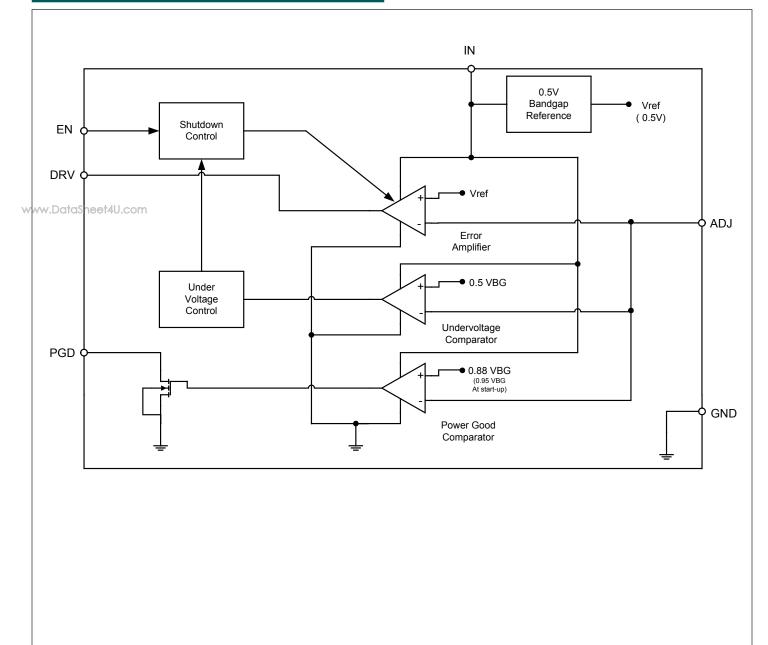

## Block Diagram

#### Applications Information

#### **Theory Of Operation**

The SC339 linear FET controller provides a simple way to drive an N-channel MOSFET to produce tightly regulated output voltages from an available, higher, supply voltage. It takes its power from the 5V system supply, drawing  $130\mu A$  (typ) while operating.

It contains an internal bandgap reference which is compared to the output voltage via a resistor divider. **The resiston divider** is external and user selectable. The drive pin (DRV) can pull up to a guaranteed minimum of 4.7V. Thus, the device can be used to regulate a large range of output voltages by careful selection of the external MOSFETs (see Component Selection on this page).

The SC339 includes an active high enable control (EN). If this pin is pulled low, the drive pin is pulled low, turning off the N-channel MOSFET. If the pin is pulled up to 2.8V  $\leq V_{\rm EN} \leq V_{\rm IN}$ , the drive pin is enabled. This pin should not be allowed to float.

The SC339 has a power good output (PGD) which is an open drain output that pulls low if the related output is below the power good threshold (-12% of the programmed output voltage typical). The power good circuitry is active if the device is enabled, regardless of the state of the over-current latch.

An over-current protection circuit monitors the output voltage. If the output voltage drops below 50% (typical) of nominal, as would occur during an over-current or short condition, the device will pull the drive pin low and latch off. Toggle the power supply or enable pin to reset the latch condition.

#### **Drive Output**

The drive output is source and sink capable. The drivers both source and sink 20mA of current typically at 5V IN.

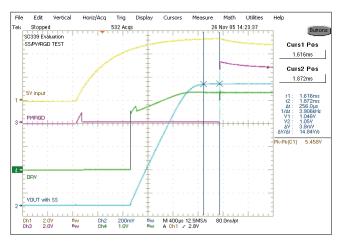

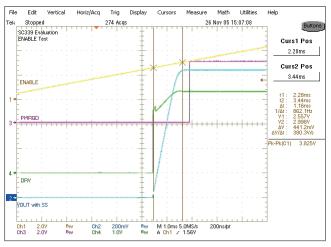

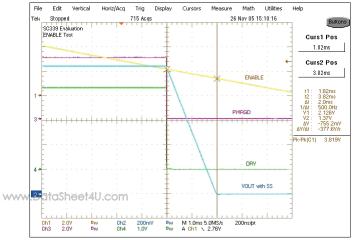

#### Soft-Start and Power Good Timing

At start-up, the internal reference is switched from its normal 0.5VDC to a 1ms (typical) linear ramp. The output voltage tracks the ramp until 0.5V is reached. The PWRGD signal is held low until the output has been in regulation approximately 500µsec to allow the output voltage to stabilize. The power-up is very smooth and monotonic.

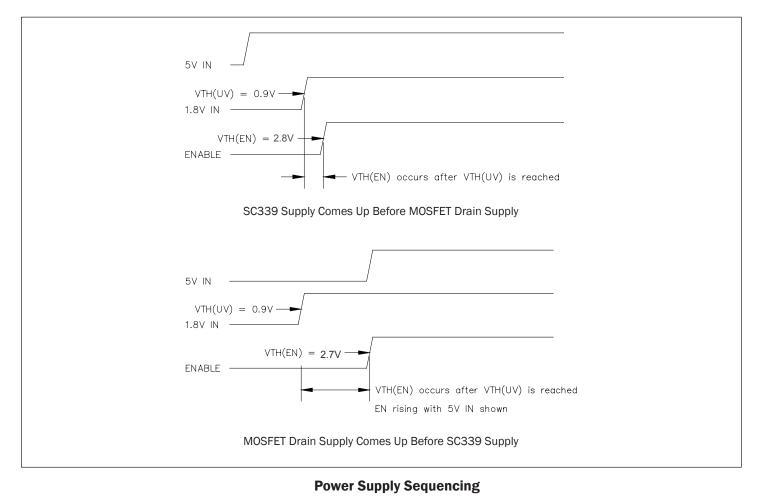

#### **OCP and Power Supply Sequencing**

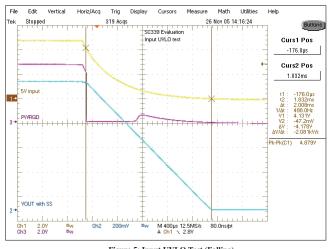

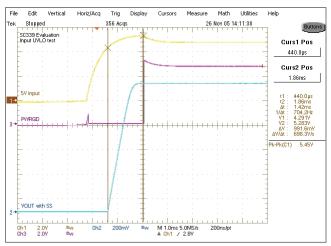

The SC339 has output under-voltage protection that looks at the output to see if it is: **a**) less than 50% (typical) of its nominal value and, **b**)  $V_{DRV}$  for that output is within 350mV (typical) of maximum. If both of these criteria are met, there is a 1ms (typical) delay and then the output is shut down. This provides inherent immunity to UV shutdown at start-up (which may occur while the output capacitors are being charged).

At start-up, it is necessary to ensure the power supplies and enable are sequenced correctly to avoid erroneous latch-off. For UV latch-off not to occur at start-up due to sequencing issues, the voltage supplied to the MOSFET drain should be greater than the output under-voltage threshold when that output is enabled. This assumes that the drop through the pass MOSFET is negligible. If not, then this drop needs to be taken into account also since:

$$V_{OUT} = V_{DRAIN} - (I_{OUT} \times R_{DS(ON)})$$

If the supply to the SC339 IN pin comes up before the supply to the MOSFET drain, then that output should be enabled after the supply to the MOSFET drain is applied - the power good signal for this rail would be ideal. If the power supply to the MOSFET drain comes up before the power supply to the SC339 IN pin, then the output can either be enabled with the supply to the IN pin or afterwards.

Please note the following example:

SC339 powered from 5V, the MOSFET ( $V_{DRAIN}$ ) powered from 1.8V, set for 1.5 $V_{OUT}$ . Worst-case: under-voltage threshold is 60% (over temperature) of 1.5V, or 0.9V. The typical enable threshold is ~2.4V, see Figure 1 on Page 7.

#### **Component Selection**

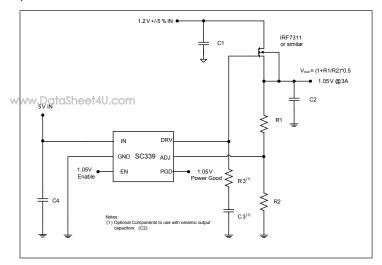

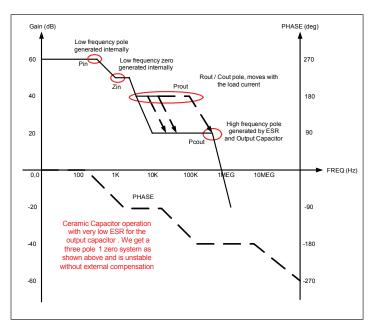

**Output Capacitors:** low ESR capacitors such as Sanyo POSCAPs or Panasonic SP-caps are recommended for bulk capacitance, with ceramic bypass capacitors for decoupling high frequency transients. Ceramic output capacitors may be used; however, use of ceramic output capacitors requires compensation on the DRV output.

#### Applications Information (Cont.)

**Input Capacitors:** placement of low ESR capacitors such as Sanyo POSCAPs or Panasonic SP-caps at the input to the MOSFET ( $V_{\text{DRAIN}}$ ) will help to hold up the power supply during fast load changes, thus improving overall transient response. If  $V_{\text{DRAIN}}$  is located at the bulk capacitors for the upstream voltage regulator, additional capacitance may not be required. In this case a 0.1µF ceramic capacitor will suffice. The 5V bias supply to the SC339 should be bypassed with a 0.1µF ceramic capacitor.

**MOSFETs:** very low or low threshold N-channel **MOSFETs** are required. Select FETs rated for V<sub>gs</sub> of 2.7V or lower. For the device to work under all operating conditions, a maximum  $R_{DS(ON)}$  must be met to ensure that the output will never go into dropout:

$$R_{\text{DSON(MAX)}} = \frac{V_{\text{IN(MIN)}} - V_{\text{OUT(MAX)}}}{I_{\text{OUT(MAX)}}} \Omega$$

Note:  $R_{_{DS(ON)}}$  must be met at all temperatures and at the minimum  $V_{_{GS}}$  condition.

**Setting The Output Voltage:** the adjust pin connects directly to the inverting input of the error amplifier, and the output voltage is set using external resistors (please refer to the Typical Application Circuit on Page 1).

Using output 1 as an example, the output voltage can be calculated as follows:

$$V_{00T} = 0.5 \cdot (1 + \frac{R1}{R2})$$

The input bias current for the adjust pin is so low that it can be safely ignored. To avoid picking up noise, it is recommended that the total resistance of the feedback chain be less than  $100k\Omega$ . With ceramic capacitors, a recommended divider current of >100µA is recommended to keep the FET conducting during light load conditions to improve transient response.

#### © 2006 Semtech Corp.

#### Applications Information (Cont.)

Table 1 lists recommended resistor values for some standard output voltages. All resistors are 1%, 1/10W.

The maximum output voltage that can be obtained from each output is determined by the input supply voltage and the  $R_{DS(ON)}$  and gate threshold voltage of the external MOSFET. Assuming that the MOSFET gate threshold voltage is sufficiently low for the output voltage chosen and the worst-case drive voltage,  $V_{OUT(MAX)}$  is given by:

www.DataSheet4U.com V<sub>OUT (MAX)</sub> = V<sub>DRAIN(MIN)</sub> - I<sub>OUT(MAX)</sub> • R<sub>DSON(MAX)</sub>

| V <sub>OUT</sub> (V) | R1 or R3 (kΩ) | R2 or R4 (kΩ) |

|----------------------|---------------|---------------|

| 1.05                 | 11.0          | 10.0          |

| 1.2                  | 14.0          | 10.0          |

| 1.5                  | 20.0          | 10.0          |

| 2.5                  | 45.3          | 11.3          |

| 3.3                  | 63.4          | 11.3          |

**Recommended Resistor Values For SC339**

#### **Design Example**

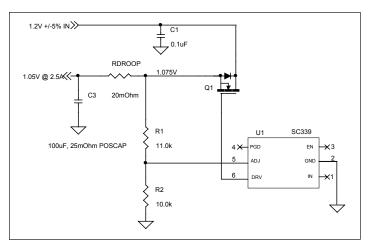

Goal: 1.05V±5% @ up to 2.5A from 1.2V±5% and 5V±5%

#### Solution 1: No Passive Droop

Total window for DC error, ripple and transient is  $\pm 52.5$  mV.

Since this device is linear and assuming that it has been designed to not ever enter dropout, there is negligible ripple on the output.

The DC error for this output is the sum of:

$V_{ADI}$  accuracy = ±1% = ±10.5mV

Feedback chain tolerance =  $\pm 1\% = \pm 10.5$ mV

Load regulation =  $\pm 0.25\% = \pm 2.6mV$

Resistors per Table 1 should be 11.0k $\Omega$  (top) and 10.0k $\Omega$  (bottom).

Total DC error = ±2.25% = 23.6mV

This leaves  $\pm 2.75\% = 28.875$ mV for the load transient ESR spike, therefore:

$$R_{ESR(MAX)} = \frac{28.875mV}{2.5A} = 11.55m\Omega$$

Bulk capacitance required is given by:

$$C_{BULK(MIN)} = \frac{dI \bullet \tau}{dV} = \mu F$$

Where dI is the maximum load current step, t is the maximum regulator response time and dV is the allowable voltage droop. Therefore with dI = 2.5A, t = 1 $\mu$ s, and dV = 28.875mV:

$$C_{\text{BULK(MIN)}} = \frac{2.5 \cdot 1 \cdot 10^{-6}}{28.875 \cdot 10^{-3}} = 87 \mu F$$

So if we use 1% V<sub>OUT</sub> set resistors we would select 100µF, 12m $\Omega$  POSCAP for output capacitance (which assumes that local ceramic bypass capacitors will absorb the balance of the (12 - 11.55)m $\Omega$  ESR requirement - otherwise 10m $\Omega$  capacitors should be used).

If we use 0.1% set resistors, then the total DC error becomes  $\pm 1.35\% = \pm 15.75$ mV, leaving  $\pm 3.65\% = 38.33$ mV for the ESR spike. In this case:

$$R_{ESR(MAX)} = \frac{38.33 \text{mV}}{2.5 \text{A}} = 15.33 \text{m}\Omega \text{ and,}$$

$$C_{BULK(MIN)} = \frac{2.5 \cdot 1 \cdot 10^{-6}}{38.33 \cdot 10^{-3}} = 65 \mu \text{F}$$

So for 0.1% resistors we could use 1 x 100 $\mu\text{F},$  15m $\Omega$  POSCAP for output capacitance.

#### Applications Information (Cont.)

This is a very severe example, since the output voltage is so low, therefore the allowable window is very small. See Solution 2 for an alternate circuit. For higher output voltages the components required will be less stringent.

The input capacitance needs to be large enough to stop the input supply from collapsing below -5% (i.e., the design minimum) during output load steps. If the input to the pass MOSFET is not local to the supply bulk capacitance then additional bulk capacitance may be wrequiredheet40.com

MOSFET selection: since the input voltage to the SC339 is  $5V\pm5\%$ , the minimum available gate drive is:

$$V_{GS} = (4.4 - 1.1025) = 3.3V$$

So a MOSFET rated for  $V_{gs} = 2.7V$  will be required, with an  $R_{DS(ON)(MAX)}$  (over-temperature) given by:

| R =       | $(V_{\text{IN(MIN)}} - V_{\text{OUT}}) =$ | $\frac{(1.14 - 1.05)}{36m\Omega} = 36m\Omega$ |

|-----------|-------------------------------------------|-----------------------------------------------|

| DSON(MAX) | I <sub>OUT(MAX)</sub>                     | 2.5                                           |

| MOSFET SELECTION         |      |               |      |  |  |

|--------------------------|------|---------------|------|--|--|

| SO-8 Footprint           |      |               |      |  |  |

|                          | Vgs  | Rds-on        | Imax |  |  |

| FDS6682                  | 1.7V | $9m\Omega$    | 14A  |  |  |

| IRF7456                  | 1.5V | $6.5 m\Omega$ | 16A  |  |  |

| 1206 Footprin            | it   |               |      |  |  |

|                          | Vgs  | Rds-on        | Imax |  |  |

| Si5406DC                 | 0.6V | 20mΩ          | 9.5A |  |  |

| NTHS5404                 | 0.6V | $25 m\Omega$  | 7.2A |  |  |

| SOT-23 Footpr            | int  |               |      |  |  |

|                          | Vgs  | Rds-on        | Imax |  |  |

| IRLMS2002                | 1V   | 30mΩ          | 5.2A |  |  |

| FDN337N                  | 0.7V | $65 m\Omega$  | 2.2A |  |  |

| (when Input<br>is > 1.2V |      |               |      |  |  |

| for 1.05V                |      |               |      |  |  |

| output)                  |      |               |      |  |  |

#### Solution 2: Using Passive Droop

Passive droop allows us to use almost the full output tolerance window for transients, therefore making the output capacitor selection simpler and less expensive. The trade-offs are the cost of the droop resistor versus the reduction in output capacitor cost, and the reduction in headroom which impacts MOSFET selection. The top of the feedback chain connects to the input side of  $R_{DROOP'}$  and the output is set for 1.075V. Thus at no load,  $V_{OUT}$  will be 1.075V (or 1.05V + 2.4%) and at  $I_{OUT}$  = 2.5A,  $V_{OUT}$  will be 1.025V (or 1.05V - 2.4%).

If 1% set resistors are used, the total DC error will be  $\pm 2.25\% = 24$  mV. Thus, at no load, the minimum output voltage will be given by:

$$V_{OUT(MIN_NO_LOAD)} = 1.075 - 0.024 = 1.051V$$

This leaves 53.5mV for transient response, giving:

$$R_{\text{ESR(MAX)}} = \frac{53.5\text{mV}}{2.5\text{A}} = 21.4\text{m}\Omega \text{ and,}$$

$$C_{\text{BULK(MIN)}} = \frac{2.5 \cdot 1 \cdot 10^{-6}}{53.5 \cdot 10^{-3}} = 47\mu\text{F}$$

Instead of 2 x 100µF, 12m $\Omega$  capacitors, we can use 1 x 47µF, 15m $\Omega$  capacitor.

#### Applications Information (Cont.)

#### **Using Ceramic Capacitors**

SC339 is capable of operation using an all-ceramic solution, needing only an external R-C compensation. The Typical Application schematic (R3, C3) from page 1 is reproduced here:

**Typical Applications Circuit**

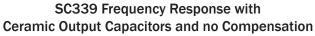

## Typical Frequency Response without Compensation and Ceramic Output Capacitors:

From this response we see that the system is not stable as it has a phase margin of approximately 0 degrees.

For stable operation we introduce a low frequency pole and a zero. The low frequency pole is used to roll off the gain quicker and the zero is used to increase the bandwidth of the system.

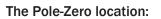

#### SC339 Frequency Response with Ceramic Output Capacitors and R-C Compensation

From the above figure we can see that the overall response of the system is stable with a decent phase margin

It is important to select the external compensation zero to be between 1 kHz and 5 kHz for optimum bandwidth and phase margin. In this example we have selected zero at approximately 3 kHz.

The compensation values are calculated by the following empirical equation:

#### $\frac{1}{2} \cdot \pi \cdot R3 \cdot C3 = 3kHz$

We chose a low R3 compensation value to roll off gain.

#### Applications Information (Cont.)

Now,

$C3 = \frac{1}{2} \cdot \pi \cdot R3 \cdot 3kHz = 530nF$

We choose C3 = 470 nF as the standard value.

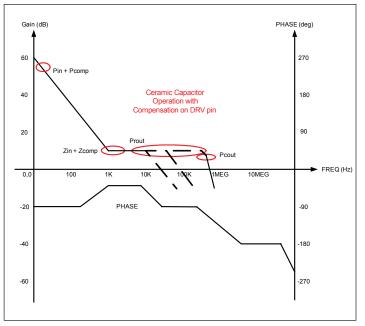

#### Soft-Start Behavior

At start-up,  $V_{OUT}$  first ramps linearly from ground at the rate of ~0.5V/ms (+/-25%) for about 800us. The linear ramping is followed by a phase of smooth settling for about 700us at the end of which the output has fully settled (to better than 1%).

#### www.DataSheet4U.com

The total start-up time of about 1.5ms is kept within 1ms - 2ms window, and this is regardless of the loading and of the external components connected to the device.

SC339 Start-Up Response

#### **Layout Guidelines**

The advantages of using the SC339 to drive external MOSFETs are:

a) that the bandgap reference and control circuitry are in a die that does not contain high power dissipating devices

and,

b) that the device itself does not need to be located right next to the power devices. Thus very accurate output voltages can be obtained since changes due to heating effects will be minimal.

The  $0.1\mu$ F bypass capacitor should be located close to the supply (IN) and GND pins, and connected directly to the ground plane.

The feedback resistors should be located at the device, with the sense line from the output routed from the load (or top end of the droop resistor if passive droop is being used) directly to the feedback chain. If passive droop is being used, the droop resistor should be located next to the load to avoid adding additional unplanned droop. Sense and drive lines should be routed away from noisy traces or components.

For very low input to output voltage differentials, the input to output/load path should be as wide and short as possible. Where greater headroom is available, wide traces may suffice.

Power dissipation within the device is practically negligible, thus requiring no special consideration during layout. The MOSFET pass devices should be laid out according to the manufacturer's guidelines for the power being dissipated within them.

## **Performance Characteristics**

Figure 1: Supply Current v/s Supply Voltage

Figure 3: Soft Start waveform shows the PWRGD delay

Figure 5: Input UVLO Test (Falling)

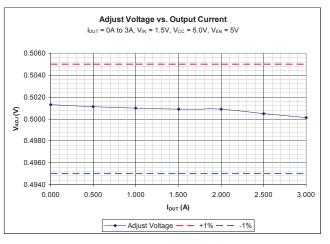

Figure 2: Adjust Voltage v/s Output Current (1% accurate)

Figure 4: Input UVLO Test (Rising)

Figure 6: Enable threshold detect (Rising)

## Performance Characteristics

Figure 7: Enable threshold detect (Falling)

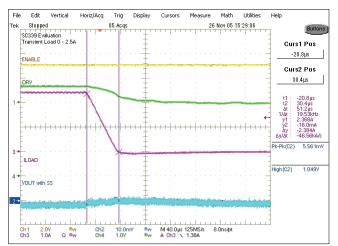

Figure 9: Transient load falling edge

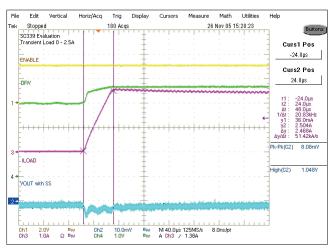

Figure 8: Transient load rising edge

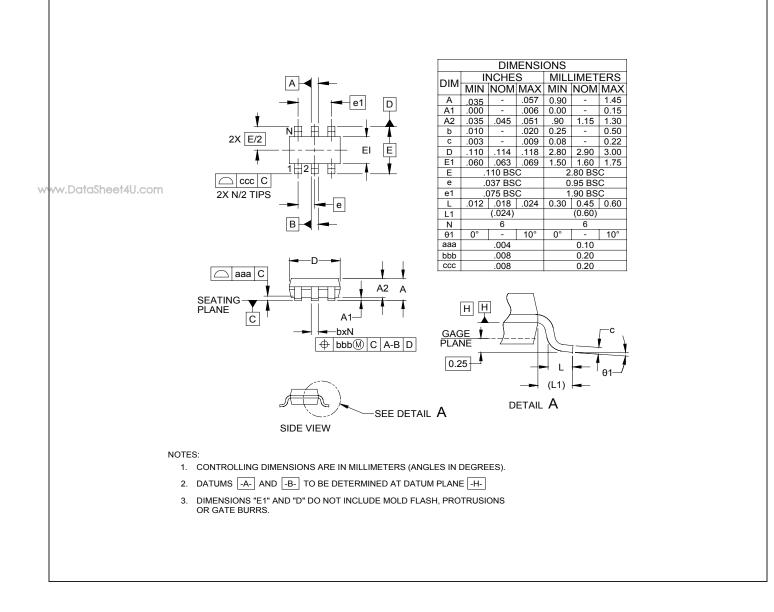

### Outline Drawing - SOT-23 6

SC339

w

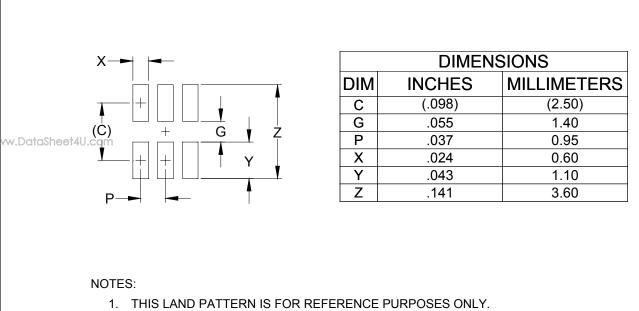

## Land Pattern - SOT-23 6

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

### **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com